虽然行业内许多人认为球栅列阵(BGA)与芯片规模包装(CSP)还是新涌现的技术,但是一些主导的电子制造商已经引入或改装了一种或两种CSP的变异技术。

BGA包装已经发展成与现在的焊接装配技术完全兼容。CSP或密间距的BGA具有的栅极间距为0.5, 0.65, 0.80mm,与其相比,塑料或陶瓷的BGA具有相对较宽的接触间距(1.50, 1.27, 1.0mm)。粗和密间距的BGA都比密间距的引脚包装IC较不容易受损坏。BGA标准允许选择地去掉接触点以满足特定的I/O要求。当建立为BGA已经建立接触点布局和引脚分布时,包装的开发者必须考虑芯片设计以及电路芯片(die)的尺寸和形状。在计划引脚分布时要遇上的其它问题是电路芯片的方向。当供应商使用板上芯片(chip-on-board)技术时,通常采用电路芯片面朝上的形式。

元件的结构在工业标准和指引中没有规定。每个制造商都将努力使其特定的结构满足顾客定义的应用。要看选作制造BGA的材料的物理特性而定,可能使用倒装芯片(flip chip)或线绑定(wire bond)技术。因为电路芯片附着结构是一种刚性材料,所以芯片绑定或附着座通常位于中心,导线将信号从芯片绑带焊盘引出到球形接触点的排列矩阵。

列阵元件的总的轮廓规格允许许多的灵活性:如引脚间距、接触点矩阵形式和结构。JEDEC MO-151 定义了一大族类的塑料BGA。方形轮廓包括了7.0~50.0mm的尺寸范围和三种接触点间距:1.50, 1.27, 和 1.0 mm。球形接触点可按偶数或奇数列和行排列的统一形式分布。虽然排列必须保持所有包装外形的对称性,但是允许元件制造上去掉接触点的位置或一个区域的触点。

密间距BGA的变量

联合电子元件工程委员会(JEDEC, Joint Electronic Device Engineering Council) 的BGA指引手册提出了许多物理特性和提供对包装供应商的形式上的灵活性。JEDEC JC-11批准的第一份有关密间距BGA的文件是以注册外形 MO-195 (the Registered Outline MO-195),基本的0.50mm间距触点排列的统一方形包装类。包装尺寸范围为4.0~21 mm,从贴装表面的总高度限定在1.20 mm。下表是考虑中的其它的变量。

| CSP标准的变量 | |

| 排列间距 | 0.40, 0.50, 0.65, 0.75, 0.80 mm |

| 触点直径 | 0.20, 0.25, 0.30, 0.40, 0.50 mm |

| 轮廓(高度)变量 | |

| (L)低轮廓 | 最大 1.70 mm |

| (T)薄轮廓 | 最大 1.20 mm |

| (V)非常薄的轮廓 | 最大 1.00 mm |

| (W)非常非常薄的轮廓 | 最大 0.80 mm |

| (U)超薄轮廓 | 最大 0.65 mm |

密间距BGA触点排列计划

球的间距和尺寸将影响电路的走线效率。许多公司已经决定对较低I/O 的CSP应用不采用0.5 mm的间距。选择一种较松散的触点,较粗的球间距可舒缓最终用户采用更复杂PCB技术的需要。

0.50 mm的排列触点间距是JEDEC推荐的最小的。触点直径规定为0.30 mm,允许误差范围为0.25~0.25 mm。可是,大多数采用0.50mm间距的BGA应用将决定于次表面电路的走线。在0.25mm焊盘之间的空间只够单个0.08mm宽线路的连线。将大量的电源和地线的触点分布在排列和局部,或空隙的的周围,去掉触点(depopulation)将提供排列矩阵的有限的贯穿。这些较高的I/O应用将依靠多层、盲通路孔、或封闭电镀焊盘内通路孔(via-on-pad)技术。

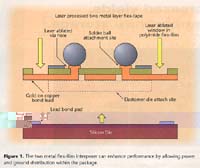

元件性能可能如包装尺寸一样相差很大。用于高密度、高I/O应用的包装技术必须首先满足周围的条件。那些使用由陶瓷或有机分层制成的刚性插入式结构的元件不能密切地配合硅芯片的外形。元件周围的引脚绑定座之间的连接必须向内流向。 µ BGA ™ 包装结构的一个实际优点是它能够提供硅芯片外形内的所有电气连接介面。一些µBGA使用高级聚酰亚胺胶片(polyimide film)作其基底结构,半添加铜电镀工艺来完成芯片上铝绑定座与聚酰亚胺插入片上球接触座之间的连接,详情见图一。不是使用普通的线绑定工艺来把芯片连接到插入片,布置在柔性插入片的镀金的铜引脚重新定形和直接绑定在芯片上。这种相顺从的材料的独特结合使元件可以经受非常苛刻的环境。

元件性能可能如包装尺寸一样相差很大。用于高密度、高I/O应用的包装技术必须首先满足周围的条件。那些使用由陶瓷或有机分层制成的刚性插入式结构的元件不能密切地配合硅芯片的外形。元件周围的引脚绑定座之间的连接必须向内流向。 µ BGA ™ 包装结构的一个实际优点是它能够提供硅芯片外形内的所有电气连接介面。一些µBGA使用高级聚酰亚胺胶片(polyimide film)作其基底结构,半添加铜电镀工艺来完成芯片上铝绑定座与聚酰亚胺插入片上球接触座之间的连接,详情见图一。不是使用普通的线绑定工艺来把芯片连接到插入片,布置在柔性插入片的镀金的铜引脚重新定形和直接绑定在芯片上。这种相顺从的材料的独特结合使元件可以经受非常苛刻的环境。

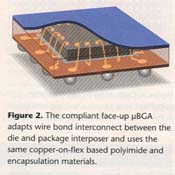

这种包装已经被几个制造商采用。定义为面朝下的(face-down)CSP,这种元件通常不比电路芯片大。芯片上的铝绑定焊盘是向着球接触点和PCB表面定位的。这种结构在业内被广泛所接受,因为材料于引脚设计的专利系统物理上相适应,补偿了硅芯片和PCB的温度膨胀系数的差别。采用顺从材料的另一个方法是将硅芯片面朝上装配。面朝上(face-up)的芯片包装为芯片附着采用了与面朝下包装一样的弹性体材料。两种概念的主要不同是在芯片与柔性胶片插入片之间的引脚端点。µBGA为电气连接采用传统的金线绑定技术。虽然由几个早期的专利保护,它的应用已经成为主流。公司要求比密间距BGA更大的包装(图二)的理由是更多的。在某些情况,通常预计新的硅产品的芯片收缩以变得比希望的和其它应用更加过分,制造商可能宁愿采用加大的接触点间距的列阵方案,以方便电路走线。

这种包装已经被几个制造商采用。定义为面朝下的(face-down)CSP,这种元件通常不比电路芯片大。芯片上的铝绑定焊盘是向着球接触点和PCB表面定位的。这种结构在业内被广泛所接受,因为材料于引脚设计的专利系统物理上相适应,补偿了硅芯片和PCB的温度膨胀系数的差别。采用顺从材料的另一个方法是将硅芯片面朝上装配。面朝上(face-up)的芯片包装为芯片附着采用了与面朝下包装一样的弹性体材料。两种概念的主要不同是在芯片与柔性胶片插入片之间的引脚端点。µBGA为电气连接采用传统的金线绑定技术。虽然由几个早期的专利保护,它的应用已经成为主流。公司要求比密间距BGA更大的包装(图二)的理由是更多的。在某些情况,通常预计新的硅产品的芯片收缩以变得比希望的和其它应用更加过分,制造商可能宁愿采用加大的接触点间距的列阵方案,以方便电路走线。

采用BGA的PCB设计指南

在JEDEC95出版物中提供了栅格列阵包装的外形。列阵包装元件的总的外形规格允许很大的灵活性,包括引脚间距、触点矩阵形式和结构。JEDEC标准允许芯片附着在介面结构的任何一面。

接触点矩阵选项。接触点可以统一的形式分布;可是,矩阵总是以包装的中心线对称的。允许不同的制造商减少接触点,分布形式通常描述为:全偶矩阵(full-even matrix)、全奇矩阵(full-odd matrix)、周围矩阵(perimeter matrix)或交错矩阵(staggered matrix)。

全矩阵(full matrix)。对一个给定的包装尺寸,有两种全矩阵的可能性:偶数或奇数。其中之一是理论上能够适合于包装上的、给定尺寸和触点间距的最大矩阵。另一个矩阵是一行乘一列的较小矩阵。

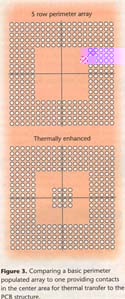

周围矩阵(perimeter matrix)。周围矩阵是去掉矩阵中央的触点排列,它不影响矩阵的中心线。一个温度上改进的矩阵是周围排列矩阵,在矩阵的中心区域再增加触点(图三)。

周围矩阵(perimeter matrix)。周围矩阵是去掉矩阵中央的触点排列,它不影响矩阵的中心线。一个温度上改进的矩阵是周围排列矩阵,在矩阵的中心区域再增加触点(图三)。

较低I/O的元件可能受惠于采用其中一种密间距BGA。通过选择性地去掉触点,仍然保持基本的0.50mm栅格,这可能更实际地使电路走线通道达到最大。在较低的I/O元件上触点之间的间隙越宽,通常可接纳电路的表面走线。

交错矩阵(staggered matrix)。其定义是每隔一个去掉一个触点的一种空隙布局。它提供一个有效的最小的、全矩阵间距n倍的中心对中心间距。为了保持A1接触点位置,交错矩阵必须使用全奇矩阵方式来开发。

选择性减少触点(selective depopulation)。除了上述的矩阵减少触点方法之外,触点也可以选择性的去掉。选择性的减少触点可以任何方式完成,只要不把矩阵移出包装外形的中心。

附着座(attachment site)的计划

附着座(attachment site)的计划

推荐用于BGA的附着座或焊盘的几何形状是圆形的,其直径应该适应接触点的间距和尺寸变化。焊盘的直径不应该大于调节到满足触点间距和尺寸所要求的直径。焊盘的直径不应该大于包装介面上焊盘的直径,通常比规定的球形触点的名义直径小10%。在最后定出焊盘分布排列和几何形状之前,参阅IPC-SM-782第14.0章和制造规格文件。两种方法用来定义附着座:焊盘或铜片定义和阻焊定义(图四)。

铜片定义焊盘布局(copper defined land pattern)。腐蚀的铜片定义这些焊盘布局。阻焊间隔应该距离腐蚀的铜片焊盘至少0.075mm。

阻焊定义焊盘布局(soldermask defined land pattern)。如果使用阻焊定义布局,将焊盘直径相应调整以保证阻焊的覆盖。

列阵元件的电路走线

PCB次表层的信号走线通道将受保留给通孔焊盘座之间的空隙的限制。设计者可通过增加更多的电路层来选择一种更充分的空间,但是,当设计要求是使用更细线宽和更近空隔的、更高密度的电路走线时,那么电路板会更难制造,增加总的生产成本。采用微型密间距排列元件的电路密度通常比采用较大间距塑料BGA的电路密度要高。次表层的走线应该考虑用作大部分的信号线路,因为它将为更复杂的元件提供最有效的电路走线。

虽然可以减少增加电路层的需要,采用更细的线和空隙可能会增加成本,因为制造效率更低。用于制造多层电路板的交替高密度和微通路孔制造技术目前只有有限的资源。当计划内部连接结构时应该考虑这些技术。用较宽的接触点间距来对BGA元件布线,困难会较少。对那些采用减少排列或宽间距的元件,电路布线的限制较少。对许多低I/O产品,电路布线经常可以在贴装结构的外表面提供。

通路孔的(via hole)计划

为了使钻孔的速度最大,保持较低的钻孔破损率,大多数电路板制造商宁愿减小最后孔的尺寸,但不小于PCB总厚度的1/3。对密间距BGA元件的走线所要求的更细的几何形状和更密的电路密度,将鼓励设计者考虑小的通路孔和每个孔周围的环,以下是通常所推荐的(表一)。

| 表一、计划与焊盘尺寸相对应的孔的直径 | ||

| 电镀孔直径 | 焊盘直径 | 圆形环的宽度 |

| 0.50 mm(0.020") | 1.00 mm(0.040") | 0.25 mm(0.010") |

| 0.50 mm(0.020") | 0.89 mm(0.035") | 0.19 mm(0.007") |

| 0.46 mm(0.018") | 0.76 mm(0.030") | 0.15 mm(0.006") |

| 0.38 mm(0.015") | 0.63 mm(0.025") | 0.12 mm(0.005") |

| 0.33 mm(0.013") | 0.50 mm(0.020") | 0.08 mm(0.003") |

| 0.25 mm(0.010") | 0.50 mm(0.020") | 0.13 mm(0.005") |

| 0.20 mm(0.008") | 0.50 mm(0.020") | 0.15 mm(0.006") |

| 0.20 mm(0.008") | 0.46 mm(0.018") | 0.13 mm(0.005") |

| 0.20 mm(0.008") | 0.40 mm(0.016") | 0.10 mm(0.004") |

| 0.20 mm(0.008") | 0.35 mm(0.014") | 0.075 mm(0.003") |

密间距BGA的焊盘形式/通路孔的计划

为了接纳电路走线路线,保持在内层的通路孔焊盘可减少到0.25mm(0.010")的直径或方形。对于高I/O的芯片规模BGA应用,可能有必要权衡相对于较小电路特性的增加电路层的成本。因为小于或等于0.8mm的密间距BGA包装的焊盘排列可能占用元件下面大部分表面,电路的走线通道受到限制。对具有高接触点密度的元件,大部分信号走线必须重新分配给主介面结构的其它电路层。当采用刚性多层PCB方法时,高I/O元件的信号走线应该通过盲电镀通路孔传送到至少一个次表面电路层。理想地,盲通路孔是在叠层之后钻孔的,但当电路密度很高时,盲孔和埋入式通路孔两者都是实际的解决方案(表二)。在附着座内钻的通路孔必须密合地堵塞或电镀。如果通路孔的钻孔穿过整个电路结构,那么将有相当量的焊锡合金在装配过程中从接触座迁移走。

|

表二、计划微型通路孔与焊盘相适应的直径 | ||||||

|

外层焊盘直径 |

通路孔名义尺寸 |

内层焊盘直径 |

接触点间距 |

线数/间隙 | ||

|

4/4* |

3/3* |

2/2* | ||||

|

0.50mm(0.020") |

0.15mm(0.006") |

0.25mm(0.010") |

1.00mm |

3 |

4 |

7 |

|

0.40mm(0.016") |

0.15mm(0.006") |

0.25mm(0.010") |

0.75mm |

2 |

2 |

4 |

|

0.30mm(0.012") |

0.13mm(0.005") |

0.20mm(0.008") |

0.50mm |

1 |

1 |

2 |

|

0.30mm(0.012") |

0.10mm(0.004") |

0.18mm(0.007") |

0.50mm |

1 |

1 |

2 |

|

0.25mm(0.010") |

0.10mm(0.004") |

0.18mm(0.007") |

0.50mm |

1 |

1 |

2 |

|

0.25mm(0.010") |

0.08mm(0.003") |

0.15mm(0.006") |

0.50mm |

1 |

1 |

3 |

|

0.20mm(0.008") |

0.08mm(0.003") |

0.15mm(0.006") |

0.50mm |

1 |

1 |

3 |

|

0.20mm(0.008") |

0.05mm(0.002") |

0.10mm(0.004") |

0.50mm |

1 |

2 |

3 |

|

* 数字代表 mil | ||||||

为了提供走线导体的迹线和保证一个可接受的空气间隙,设计者可以为通路孔选择方形的焊盘。方形结构保持足够的铜箔在焊盘对角线的角上以补偿正方形各边减少的环形截面。方形的通路孔可以在必要时靠得较近。在一个移建立的栅格上,可能在焊盘之间走两或三条导线。通过使用小的0.25mm(0.010")的方形通路孔焊盘和实心或盲通路孔,设计者可将电路走线传给内层,以接纳CSP所需的较高走线密度。

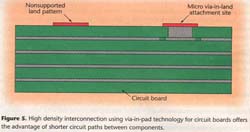

机械钻孔和电镀孔达到一个经济上有限的最小直径0.20~0.25mm。三种最常见的微型通路孔的制造技术是:激光钻孔(laser drilling)、光刻蚀法(photolithography)和等离子蚀刻(plasma etching)。三种工艺中,激光是商业上使用最多的技术。激光钻孔受欢迎的理由包括:不要求特殊的材料和设备,制造效率高。激光钻孔虽快,但还是比转轴钻孔(spindle drilling)慢。并且因为板是单块地而不是叠层钻孔,所以单价相当高许多。小型或微型通路孔的化学或等离子钻孔也是一个考虑。小型通路孔成形的最经济的方法是使用照片感光和集结(增加铜)成形技术,如图五所示。与现有的使用机械钻孔和电镀通路孔的PCB制造方法相比较,微型通路孔的生产占PCB市场的较小份额。

机械钻孔和电镀孔达到一个经济上有限的最小直径0.20~0.25mm。三种最常见的微型通路孔的制造技术是:激光钻孔(laser drilling)、光刻蚀法(photolithography)和等离子蚀刻(plasma etching)。三种工艺中,激光是商业上使用最多的技术。激光钻孔受欢迎的理由包括:不要求特殊的材料和设备,制造效率高。激光钻孔虽快,但还是比转轴钻孔(spindle drilling)慢。并且因为板是单块地而不是叠层钻孔,所以单价相当高许多。小型或微型通路孔的化学或等离子钻孔也是一个考虑。小型通路孔成形的最经济的方法是使用照片感光和集结(增加铜)成形技术,如图五所示。与现有的使用机械钻孔和电镀通路孔的PCB制造方法相比较,微型通路孔的生产占PCB市场的较小份额。

密间距BGA装配工艺的发展

如果一间公司正达到可接受的SMT装配效率的话,它不应该再要求额外的资源来实施BGA技术。在传统的SMT装配工艺基础上唯一的推荐是BGA贴装之前的锡膏印刷检查。

锡膏印刷、贴片和回流焊接过程和用于密脚装配的一样,可是,使用者都说BGA的工艺缺陷较少。BGA的模板夹具将保持用于密脚引脚应用的许多特征和技术,许多装配也保持密脚元件的。一项改进锡膏转移到小型焊盘几何形状上的技术是锥形焊盘开口。对较大间距BGA的开口不象密间距使用的那么小,但锡膏的释放同样是关键。模板的开口可等于焊盘的直径或调整到满足特殊的要求。把模板开孔做大可能增加锡桥。

装配所需的特征

有共晶焊锡接触点的BGA和CSP在回流焊接过程中回自己定位,因此贴装精度不象密脚引脚型元件那么关键。还有,表面装配系统上为密脚发展起来的视觉定位技术用于BGA的应用是绰绰有余。为了提高贴装精度,装配专家可能在那些密脚元件的附近定义一或两个基准特性。基准目标允许贴装系统补偿PCB制造误差的角度变化和收缩因素。基准点的尺寸通常为1.0mm的直径。为了保证基准目标的识别,目标应该没有阻焊材料。如果要采用较小的目标,如0.5mm直径,那么先确认设备能力,因为不是所有的视觉系统可识别较小的几何图形。可能的话,阻焊的空隔应该等于基准点的半径。另外,基准点内外的背景应该统一。

回流焊接过程

强制空气/气体和红外焊接两者都可用于BGA的回流焊接。由于大多数的焊接点都是不能视觉检查的,焊锡材料液态的温度和居留时间是关键的。共晶焊锡要求115°C~120°C的温升来将锡膏中的助焊剂排出和保证提供可靠焊接点所需要的熔湿特性。

BGA的回流曲线与焊接密脚元件使用的是一样的。

元件定位。看上去定位不准的元件在回流期间回自己对中,不应该用手去调节。

除了与装配有关的问题之外,必须考虑第二个步骤。许多用于引脚型表面贴装装配的测试和检查技术可能不能直接用于BGA装配。

BGA装配的测试

需要开发新的故障查找方法和技术,因为单个触点或网的探测是困难的。

返工与返修。已开发出拆卸工艺。只有新元件应该用免洗助焊剂装配。

检查方法。可用X光来确认焊锡回流,百分之百的检查可能是不实际的和没有必要的。

BGA焊接过程的检验

在工艺开发过程中,BGA下面的焊锡连接的最终状态可能是一个关注。产品的可靠性是个关键的问题,必须用行业认可的方法加以确认。焊接点的实际测量、轮廓或形状可用破坏性的和非破坏性的技术得到。破坏性的要求穿过焊接点作元件的截面图。在产品投入生产后,焊锡检查的其它非破坏性的方法可能是较为实际的,例如,X光。对装配的关键部分作X光检查已证明是监测过程的非常有效的方法。X光检查可容易地发现接触点之间的锡桥、陷于元件下面的锡渣和焊锡不足。后者更难测量,因为锡球的图象本身将支配监视下的焦点。

对焊接过程品质和一致性的控制最有利的是BGA元件贴装之前的锡膏检查。不象翅形引脚元件,焊接返工是不容易的,将元件卸下通常是纠正严重焊接缺陷的唯一方法。印刷检查应该包括厚度和覆盖区域的测量。使用较高级的电路板材料和与表面处理相适应的工艺,将对装配效率有很大帮助。PCB设计也将影响装配效率和产品可靠性。最重要的是,确保一致和连续的锡膏的应用。与严格的过程监测一起,可减少BGA的焊接缺陷到一个和高I/O密间距引脚型元件相比戏剧性低的水平。

较小的BGA包装外形可让使用者满足用引脚型元件不可能达到的尺寸减少目标。因为BGA和CSP是一种完全测试的元件并完全与表面贴装技术兼容,所以该包装可能涌现在制造的主流中,而只有很少或不需要专门的处理。使用者承认BGA和密间距CSP元件正提供一个稳固的、高效率的装配过程。虽然今天市场上大多数BGA元件具有可能大于0.80mm的接触间距,但许多公司仍处在减小产品尺寸和维持元件之间更短路线的压力之中。当BGA元件与密间距引脚元件比较时,大多数装配工艺专家宁愿选择高低不平的锡球接触点,而不是脆弱的引脚。

Vern Solberg, can be contacted at Solberg Manufacturing Technology, (408) 741-1231; E-mail: vesolberg@aol.com.

沪公网安备 31011502005504号

沪公网安备 31011502005504号