驱动力

受到携带微型电话、传呼机和个人辅助用品的人的数量增加的驱动,消费电子工业近来非常火爆。变得更小、更快和更便宜的需要驱动着一个永不停止的提高微型化的研究技术的需求。大多数微型电话有关的制造商把0201实施到其最新的设计中,在不久的将来,其它工业领域也将采用该技术。在汽车工业的无线通信产品在全球定位系统(GPS, global positioning systems)、传感器和通信器材中使用0201技术。另外,公司在多芯片模块(MCM, multi-chip module)中使用0201技术,以减少总体的包装尺寸。和这些MCM元件一起,0201技术已经更靠近半导体工业,因其直接与裸芯片包装,铸模在二级电路板装配的包装内。必须完成许多研究,以定义出焊盘设计和印刷、贴装、回流的工艺窗口,从而在全面实施0201之前达到高的第一次通过合格率和高的产量。

电路板设计指引

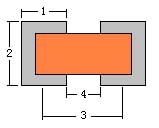

已经有几个对采用0201无源元件的电路板设计指引的研究。大部分通过变化焊盘尺寸、焊盘几何形状、焊盘对焊盘间距和片状元件与元件的间距,来观察设计。重要的设计方面包括缺陷最小化和增加元件密度,同时收缩整个印刷电路板的尺寸。以下是可能受焊盘设计所影响的主要缺陷:

- 墓碑(Tombstoning) 该缺陷的发生是当元件由于回流期间产生的力而在一端上面自己升起的时候。通常,墓碑发生是由于元件贴装在相应的焊盘上不平衡,一端的焊锡表面能量大于另一端。表面能量的不平衡引起一端的扭矩更大,将另一端拉起并脱落焊盘。小于0603的元件比较大的无源元件更容易形成墓碑。对0402和0201元件,焊盘设计可减少或甚至防止墓碑。焊盘横向延长,纵向减少可减少引起墓碑的纵向力。回流过程也会影响墓碑缺陷。如果升温坡度太大,元件的前端进入回流区可能在另一端之前熔化,将元件立起。

- 焊锡结珠(Solder beading) 焊锡球数量是一个过程指标,由于焊锡膏中使用的助焊剂而附着于无源元件,通常位于元件身体上。焊锡珠,当使用免洗焊锡膏时由于助焊剂残留和缺少其它锡膏类型通常使用的清洗步骤,是常见的,它表示过程已经偏出了工艺窗口。通常,结珠的发生是由于焊盘太靠近一起,过大的焊盘和过多的锡膏印在单个焊盘上。以高速贴装0201无源元件可能引起锡膏溅出锡膏“砖”。这些溅出的锡膏在元件周围回流,引起锡球,在IPC 610 中定义为缺陷。这是超小无源元件上最常见的缺陷。如上所述,设计指引可以用来控制这些类型的缺陷,以及理解工艺窗口。有人推荐,0201焊盘设计来限制锡膏在元件长边上的接触角,而延长焊盘的横向尺寸,允许更大的接触角1,2,3。与这种焊盘设计相关的力将趋向于作用在元件侧面,允许更多的自己对中,而减少引起“墓碑”的力。

焊盘间隔也可能控制焊锡球化缺陷。研究表明,焊盘中心对中心应该在0.020~0.022"之间,边对边的间隔大约为0.008~0.010"。焊盘设计应该达到贴装工具的精度。另有研究表明,对于无源元件,沿纵向轴的恢复力比较大,但如果元件贴装有纵向偏移,那么该元件必须与两个焊盘接触,保证两个不同的力来自己定位。因此,如果贴装机器只有0.006"的精度,贴出0201的偏移太大,那么元件将不会自己定位。表一列出了推荐用来减少墓碑和焊锡结珠的焊盘尺寸和设计。

| 表一、0201焊盘设计推荐 | |||

| 0201焊盘尺寸 | 下限 | 上限 | 过程效果 |

| 长度尺寸 | 0.010" | 0.012" | 改进“墓碑” |

| 宽度尺寸 | 0.016" | 0.018" | |

| 焊盘间隔() | 0.020" | 0.022" | 改进焊锡结珠 |

| 焊盘间隔() | 0.008" | 0.010" | |

| |||

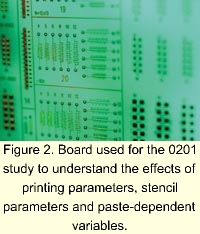

不幸的是,只有很少的出版数据解释对于其它电路板设计变量,特别是元件对元件间距的限制,工艺窗口在哪里。元件间距可受各种因素影响,如板的放置和0201元件的贴装。为了理解设计指引的工艺窗口,一项非常广泛的研究正在进行中*。用于该研究的板如图二所示。设计包括各种焊盘尺寸,元件方向( 0°, 90°和±45°),元件间距(0.004, 0.005, 0.006, 0.008, 0.010 和 0.012"),连到焊盘的迹线厚度(0.003, 0.004 和 0.005")。0201焊盘名义尺寸为0.012 x 0.013" ,和变动 0, 20 和 30%。焊盘到焊盘间隔为0.022"。0201元件分别贴放靠近其它的0201, 0402, 0603, 0805 和 1206,元件间距如上所述。迹线厚度是有变化的,对0201和0402两者,都有两个焊盘之一位于地线板上。这是要调查无源元件对吸热的影响。

不幸的是,只有很少的出版数据解释对于其它电路板设计变量,特别是元件对元件间距的限制,工艺窗口在哪里。元件间距可受各种因素影响,如板的放置和0201元件的贴装。为了理解设计指引的工艺窗口,一项非常广泛的研究正在进行中*。用于该研究的板如图二所示。设计包括各种焊盘尺寸,元件方向( 0°, 90°和±45°),元件间距(0.004, 0.005, 0.006, 0.008, 0.010 和 0.012"),连到焊盘的迹线厚度(0.003, 0.004 和 0.005")。0201焊盘名义尺寸为0.012 x 0.013" ,和变动 0, 20 和 30%。焊盘到焊盘间隔为0.022"。0201元件分别贴放靠近其它的0201, 0402, 0603, 0805 和 1206,元件间距如上所述。迹线厚度是有变化的,对0201和0402两者,都有两个焊盘之一位于地线板上。这是要调查无源元件对吸热的影响。

印刷

许多存在于印刷先进技术包装,如CSP、微型BGA和倒装芯片等,的同样的问题与规则对0201元件的印刷是同等重要的。对那些比其它板上元件小几倍的开孔,使用较厚的模板和相同的锡膏进行印刷几乎是不可能的。有关0201工艺的普遍提出的问题包括模板厚度、开孔的尺寸、锡膏类型和要求的开孔几何形状。

现在,了解锡膏如何从不同厚度模板的各种开孔尺寸和几何形状中释放的工作正在进行中。该课题研究的一个主要方面就是在决定稳定的印刷窗口时面积比率的重要性。面积比率(area ratio)是开孔的横截面积除以开孔壁的面积。较早前的研究表明,在决定稳定的工艺窗口时,面积比率提供了比模板宽度开孔减少法(stencil-wide aperture reduction methods),如纵横比(aspect ratio),高得多的精度。该研究得出了大约0.6和更高的面积比可以沉淀锡膏的体积很接近开孔的总体积。

从进行中研究的试验性丝印数据显示,0.005"的模板,0.49的面积比率的0.096 x 0.0104" 的焊盘,对第四类型的Sn/Pb锡膏的释放性能很差。可是,0.56面积比的0.0108" x 0.0117" 的开口尺寸提供比较好的锡膏量和释放性能。而现在很少有发表的有关0201的丝印过程的数据,存在的东西都是模糊的,只说模板越薄越好,第四类锡膏(比第三类颗粒小)对锡膏释放的表现较好。可是,由于第四类比第三类更稀,使用第四类对印刷其它的SMT元件可能不行,因为材料塌落。该研究是用来理解印刷参数、模板参数和锡膏有关变量的影响。用于丝印过程的变量在表二中列出。

| 表二、DOE Variables for Screeening Study | ||||||||||||||||||||||||

|

Stencil Printing Screening | ||||||||||||||||||||||||

| ||||||||||||||||||||||||

|

Stencil Printing DOE | ||||||||||||||||||||||||

| ||||||||||||||||||||||||

|

Variable to be Held Constant | ||||||||||||||||||||||||

|

理解和比较诸如锡膏沉积量和焊锡结珠缺陷的变量,要求许多贴装和反复过程。理解对于可能小如0.010"开口,锡膏如何表现,在控制和实施0201印刷工艺时是很重要的。

贴装

在整个0201工艺中贴装可以认为是最重要的一环。因为贴装系统从供料系统吸取0201元件,视觉识别和准确地贴装元件,在设定这个过程中必须小心。基本上,0201贴装过程涉及四个分开的运作:

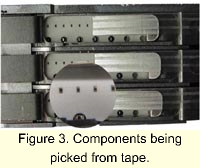

首先从送料器吸取元件。最常见的,0201无源元件包装在纸带上,8mm宽纸带上的凹坑装纳元件。图三详细地表示出元件是怎样从纸带吸取的。当设定吸取过程时,必须注意到细节。因为0201只是自从1999年才作为SMT工艺的元件,生产元件和送料带的误差问题仍然存在。虽然在带上似乎包装得紧密,在微米级,但是实际上相当松散。使用几乎与元件一样大的吸嘴,误吸的机会可能高。因为这个理由,吸嘴通常制造得比元件稍微大一点。

首先从送料器吸取元件。最常见的,0201无源元件包装在纸带上,8mm宽纸带上的凹坑装纳元件。图三详细地表示出元件是怎样从纸带吸取的。当设定吸取过程时,必须注意到细节。因为0201只是自从1999年才作为SMT工艺的元件,生产元件和送料带的误差问题仍然存在。虽然在带上似乎包装得紧密,在微米级,但是实际上相当松散。使用几乎与元件一样大的吸嘴,误吸的机会可能高。因为这个理由,吸嘴通常制造得比元件稍微大一点。

- 一旦吸取到元件,真空检查决定元件的存在或不存在。这是检查的一个重要方面,因为如果元件不存在,贴装头必须处理掉无吸的0201或再吸取元件。吸取错误一般不直接影响实际的过程,但会影响总的处理时间和产量。现时的研究也评估了带与盘(tape-and-reel)、Surf tape和最后的散装盒(bulk-case)送料的区别。

- 一旦通过真空检查确认元件的存在,视觉系统将元件定位到电路板。高级的视觉系统可完成元件的外形测量或识别两个元件端。为了做到这一点,视觉系统决定是否元件附着在吸嘴上不正确或是否超出可靠的元件与贴装所要求的公差。如果元件超出公差,则被放弃。

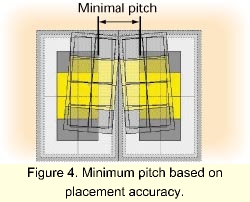

最后步骤是将0201贴装到焊盘的焊锡内。虽然这个过程必须快速完成,但也必须准确,以保证元件完全贴放在各个焊盘上。如果元件贴放不准确,诸如墓碑或相邻元件之间的锡桥等缺陷机会戏剧性地增加。当考虑使用0201元件设计电路板的最小元件间距的时候,贴装系统的精度也应该考虑。图四表示在贴装精度的基础上,应该使用的最小间距。例如,如果贴装系统的精度为±45µm,那么应该设定大约90µm的最小间距。

最后步骤是将0201贴装到焊盘的焊锡内。虽然这个过程必须快速完成,但也必须准确,以保证元件完全贴放在各个焊盘上。如果元件贴放不准确,诸如墓碑或相邻元件之间的锡桥等缺陷机会戏剧性地增加。当考虑使用0201元件设计电路板的最小元件间距的时候,贴装系统的精度也应该考虑。图四表示在贴装精度的基础上,应该使用的最小间距。例如,如果贴装系统的精度为±45µm,那么应该设定大约90µm的最小间距。

贴装力与速度也是重要的贴装过程方面。因为每台机器都不同,必须定出特性,保证速度够快以保持焊锡不从锡膏砖溅出,使用的力不至于将元件过分压入锡膏。如果使用太大的力或太高的速度,会增加焊锡球或元件偏移的可能性。

贴装课题评估速度、力量和降低限制。通常,速度和力是依赖机器的,但对精度,焊锡熔湿与自我定位力等物理现象是不依赖机器的,因此平台与平台之间都是一致的。数据显示,如果使用较早前所提及的焊盘设计,长度方向的贴装偏移将比宽度方向的偏移允许更多的自我定位。长度方向过多的偏移产生比宽度方向更多的缺陷。回流焊接之后的元件偏移是宽度方向偏移引起的较常见的缺陷。

回流焊接

回流0201元件与回流稍微较大的0402没有大的差别;可是必须注意0201回流过程使用的温升率。用大的预热斜度处理0201元件可能增加墓碑的机会。大于每分钟2°C的坡度可能引起元件一端的锡膏稍微比另一端回流快。如果元件一边首先回流,不平衡力将作用在元件上,由于表面张力,在首先回流焊盘的方向上立起元件。

回流过程的另一方面是空气与氮气的使用。资料显示使用空气可减少大多数缺陷4,5。因为焊锡在氮气中比在空气中熔湿较好,使用空气环境减少熔湿,允许时间将元件两头熔湿更一致。研究采用的变量如表三所示,在三个级别上参数的变化,以理解其对焊接点质量和其它过程有关缺陷的影响。

| 表三、Reflow DOE Variables Reflow Screening | |||||||||||||||

| |||||||||||||||

| Reflow Parametric Study | |||||||||||||||

|

结论

完全地理解0201过程是不可能的。在未来几年内,将会进行无数的研究,带着理解所有可能的过程和设计因素的目标,来考察0201过程。因为每个过程单元有如此之甚的变量依赖于其它因素,很难找到一个满足所有可能的过程问题的答案。随着SMT的进步,新的技术改革将要求通过研究去找到工艺窗口和适当的电路板设计。

* 由西门子和乔治亚工学院实施的联合课题研究。

- REFERENCES

- J.H. Lau, Flip Chip Technologies, McGraw-Hill, 1995.

- Internal Siemens preliminary research results.

- M. Yuen, H. Benedict, K. Havlovitz and T. Pitsch, Plexus Electronic Assembly Corp., and A.C. Mackie, Praxair Inc., "Tombstoning of 0402 and 0201 Components: A Study Examining the Effects of Various Process and Design Parameters on Ultra-small Passive Devices," referenced www.plexus.com.

- J.H. Adriance and J.D. Schake, "Mass Reflow Assembly of 0201 Components," APEX 2000 Proceedings, P-EQ4/3-1, April 2000.

- G.D. Rodriguez, "Analysis of the Solder Paste Release in Fine-pitch Stencil Printing Processes," Georgia Institute of Technology Master's Thesis, June 1998.

BRIAN J. LEWIS, may be contacted at Siemens EAE, 2875 Northwoods Pkwy., Norcross, GA 30072; (404) 894-6351; Fax: (404) 875-0668; E-mail: brian.lewis@eae.siemens.com. Paul Houston may be contacted at the Manufacturing Research Center at the Georgia Institute of Technology; (404) 894-2793; E-mail: paul.houston@marc.gatech.edu.

沪公网安备 31011502005504号

沪公网安备 31011502005504号