充胶的有效使用要求掺和许多的因素,包括产品设计问题,来适应充胶工艺和产品需要。

随着电路的密度增加和产品形式因素的消除,电子工业已出现许许多多的新方法,将芯片级(chip-level)的设计更紧密地与板级(board-level)装配结合在一起。在某种程度上,诸如倒装芯片(flip chip)和芯片级包装(CSP, chip scale package)等技术的出现事实上已经模糊了半导体芯片(semiconductor die)、芯片包装方法与印刷电路板(PCB)装配级工艺之间的传统划分界线。虽然这些新的高密度的芯片级装配技术的优势是非常重要的,但是随着更小的尺寸使得元件、连接和包装对物理和温度的应力更敏感,选择最好的技术配制和达到连续可靠的生产效果变得越来越困难。

改善可靠性的关键技术之一就是在芯片与基板之间填充材料,以帮助分散来自温度变化和物理冲击所产生的应力。不幸的是,还没有清晰的指引来说明什么时侯应使用充胶和怎样最好地采用充胶方法满足特殊的生产要求。本文将探讨有关这些问题的一些最近的想法。

为什么充胶?

考虑使用底部灌充密封胶的最初的想法是要减少硅芯片(silicon die)与其贴附的下面基板之间的总体温度膨胀特性不匹配所造成的冲击。对传统的芯片包装,这些应力通常被引线的自然柔性所吸收。可是,对于直接附着方法,如锡球阵列,焊锡点本身代表结构内的最薄弱点,因此最容易发生应力失效。不幸的是,它们也是最关键的,因为在任何连接点上的失效都将毁灭电路的功能。通过紧密地附着于芯片,焊锡球和基板,填充的材料分散来自温度膨胀系数(CTE, coefficient of thermal expansion)不匹配和对整个芯片区域的机械冲击所产生的应力。

充胶的第二个好处是防止潮湿和其它形式的污染。负面上,充胶的使用增加了制造运行的成本,并使返修困难。由于这一点,许多制造商在回流之后、充胶之前进行快速的功能测试。

决定何时充胶

因为存在不下五十种不同的CSP设计1,加上无数的变量与涉及连接设计的操作条件,所以很难提供一个确切的规则决定何时使用充胶。可是,在设计PCB时有许多关键因素应该考虑进去。一些重要因素包括:

- 芯片与基板之间温度膨胀系数(CTE)的不同。硅的CTE为2.4 ppm;典型的PCB材料的CTE为16 ppm。陶瓷材料可以按匹配的CTE来设计,但95%的矾土陶瓷的CTE为6.3 ppm。充胶在基于PCB的包装上需要较大,虽然在陶瓷基板上也显示充胶后的可靠性增加。一个替代方法是使用插入结构的基板,如高CTE的陶瓷或柔性材料,作为芯片与主基板之间的吸振材料,它可减轻PCB与硅芯片之间的CTE差别。

- 芯片(die)尺寸。通常,芯片面积越大,应力诱发的问题越多。例如,一项研究表明,当芯片尺寸由6.4增加到9.5mm时,连接所能忍受的从-40 ~ 125°C的温度周期的数量由1500次减少到900次2。

- 锡球尺寸与布局在充胶评估上扮演重要角色,因为较大的球尺寸,如那些CSP通常采用的300µ的直径,更牢固、可比那些倒装芯片(flip chip)所采用的75µ直径更好地经受应力。假设CSP与倒装芯片的一个两元焊接点的相对剪切应力是相似的,那么CSP焊接点所经受的应力大约为倒装芯片的四分之一。因此,CSP的设计者认为焊锡球结构本身可以经得起基板与芯片温度膨胀所产生的机械应力。后来的研究2显示充胶(underfill)为CSP提供很高的可靠性优势,特别在便携式应用中。在布局问题上,一些设计者发现,增加芯片角上焊盘的尺寸可增加应力阻抗,但这个作法并不总是实用或不足以达到可靠性目标。

- 系统PCB厚度。经验显示较厚的PCB刚性更好,比较薄的板抵抗更大的冲击造成的弯曲力。例如,一项分析证明,将FR-4基板的厚度从0.6mm增加到1.6mm,可将循环失效(cycles-to-failure)试验的次数从600次提高到900次3。不幸的是,对于今天超细元件(ultra-small device),增加基板厚度总是不现实的。事实上,每增加一倍的基板厚度提高大约两倍的可靠性改善,但芯片尺寸增加一倍造成四倍的降级4。

- 使用环境。在最后分析中,最重要的因素通常要增加所希望的产品生命力。例如,对手携设备(手机、扩机等)的规格普遍认同的就是,在-40 ~ 125°C的温度循环1000次和从水泥地面高出一米掉落20~30次之后仍可使用正常功能。

对温度循环的研究已经显示充胶的使用可提供-40 ~ 125°C的温度循环次数增加四倍,有些充胶后的装配在多达2000次循环后还不失效5。当权衡那些暴露在越来越恶劣的环境中的设备现场失效(即退货、信誉损失等)成本时,许多制造商正积极地转向把底部充胶作为一个可靠性的保险政策。

滴胶的挑战

一旦作出决定使用充胶方法,就必须考虑到一系列的挑战,以有效的实施工艺过程,取得连续可靠的结果,同时维持所要求的生产量水平。这些关键关键问题包括:

- 得到完整的和无空洞的(void-free)芯片底部胶流

- 在紧密包装的芯片周围分配胶

- 避免污染其它元件

- 通过射频(RF)外壳或护罩的开口滴胶

- 控制助焊剂残留物。

取得完整和无空洞的胶流

因为填充材料必须通过毛细管作用(capillary action)吸入芯片底部,所以关键是要把针嘴足够靠近芯片的位置,开始胶的流动。必须小心避免触碰到芯片或污染芯片(die)的背面。一个推荐的原则是将针嘴开始点的定位在针嘴外径的一半加上0.007"的X-Y位移上,Z的高度为基板上芯片(chip)高度的80%。在整个滴胶过程中,也要求精度控制以维持胶的流动,而避免损伤和污染芯片(die)。

为了最佳的产量,经常希望一次过地在芯片多个边同时滴胶。可是,相反方向的胶的流动波峰(wave front)以锐角相遇可能产生空洞。应该设计滴胶方式,产生只以钝角聚合的波峰。

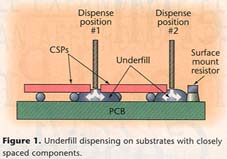

芯片数量和邻近关系 当设计一个板上有紧密包装的芯片(die)需要底部充胶时,板的设计者需要留下足够的空间给滴胶针嘴。图一所示的位置一,两个芯片共用一个滴胶路线是一个可接受的滴胶方法。与芯片边缘平行的无源元件将有挡住的作用,如图一位置二。与芯片边缘成90°位置的元件可能会把胶液从要填充的元件吸引开。无源元件周围的填充材料没有发现坏的作用。来自邻近芯片或无源元件的交叉的毛细管作用,会将填充材料从目的元件吸引开,可能造成CSP或倒装芯片底下的空洞。

当设计一个板上有紧密包装的芯片(die)需要底部充胶时,板的设计者需要留下足够的空间给滴胶针嘴。图一所示的位置一,两个芯片共用一个滴胶路线是一个可接受的滴胶方法。与芯片边缘平行的无源元件将有挡住的作用,如图一位置二。与芯片边缘成90°位置的元件可能会把胶液从要填充的元件吸引开。无源元件周围的填充材料没有发现坏的作用。来自邻近芯片或无源元件的交叉的毛细管作用,会将填充材料从目的元件吸引开,可能造成CSP或倒装芯片底下的空洞。

在大多数应用中,21或22号直径的针嘴是元件底部充胶的良好选择。较小直径的针嘴对液态流动的阻力大,其结果是滴胶速度慢。可是,有时有必要通过使用小直径的针嘴来减少圆角尺寸,保持胶流远离其它元件(表一)。

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

有时可能使用多头滴胶系统来处理这些问题,预先使用较高粘性的、不会在底下流动的材料,在相邻元件周围滴出一个堤挡。在随后的滴胶过程中,该堤挡有效地阻止任何不需要的毛细管流动到邻近元件底下。

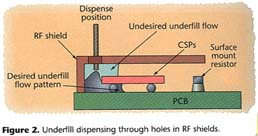

通过开口滴胶 随着底部充胶在RF装配中使用的增加,经常要挑战滴胶工艺,在RF屏蔽盖已经装配好之后来实施充胶工艺。为了最佳的生产效率,通常要考虑在其它元件贴装的同时来定位RF屏蔽盖,在一次过的回流焊接中,将所有东西焊接好。因此,产品和工艺设计者必须合作,为底部充胶在屏蔽盖上留下足够的开口。设计者还必须避免把芯片放得太靠近RF屏蔽盖,因为毛细管作用或高速滴胶可能会让填充材料流到RF屏蔽盖内和CSP或倒装芯片之上。如果元件与盖之间的间隙小,那么滴填充材料的速度将受到限制,来避免填充在元件之上。减慢滴胶速率,将减慢装配过程,限制产量。移到另一个孔或元件,又回到第一个孔滴多一些胶,这可能会有一点位移。可是,这涉及了多个运动,再一次降低产量(图二)。

随着底部充胶在RF装配中使用的增加,经常要挑战滴胶工艺,在RF屏蔽盖已经装配好之后来实施充胶工艺。为了最佳的生产效率,通常要考虑在其它元件贴装的同时来定位RF屏蔽盖,在一次过的回流焊接中,将所有东西焊接好。因此,产品和工艺设计者必须合作,为底部充胶在屏蔽盖上留下足够的开口。设计者还必须避免把芯片放得太靠近RF屏蔽盖,因为毛细管作用或高速滴胶可能会让填充材料流到RF屏蔽盖内和CSP或倒装芯片之上。如果元件与盖之间的间隙小,那么滴填充材料的速度将受到限制,来避免填充在元件之上。减慢滴胶速率,将减慢装配过程,限制产量。移到另一个孔或元件,又回到第一个孔滴多一些胶,这可能会有一点位移。可是,这涉及了多个运动,再一次降低产量(图二)。

Schwiebert和Leong给出了一个填充胶流速率的方程式7。

流动时间为:

t = 3 µL2/[h λcos(φ)]

这里:

t = 时间(秒)

µ = 流体粘度

L = 流动距离

h = 间隙或锡球高度

φ = 接触或湿润角

λ = 液体蒸汽界面的表面张力

(这些参数的值需要在液体滴胶温度,通常90°C时获得。)

大多数制造商的泵和阀可将液体送到CSP或倒装芯片,速度比材料在芯片底下可流动的较快。芯片底下液体的体积/重量还需要确定8。一旦这些数确定后,对流动速率作第一次近似计算,决定是否所以液体应该一次滴下或者小量多次滴下。典型的工艺是:当液体在第一个元件底下流动的同时,移动到第二个元件滴胶,再返回到第一个位置完成。例如,如果第一个元件的材料数量为20mg,并分成两个滴胶周期,那么必须要一个可准确滴出10mg数量的滴胶系统。

控制助焊剂残留

经验显示,存在过多的助焊剂残留可能对充胶过程有负面的影响。这是因为填充材料附着于助焊剂残留,而不附着于所希望的锡球、芯片和基板,造成空洞、拖尾和其它不连续性。而有研究6表明,在滴胶填充之前清洁芯片底部可看到温度循环改善达五倍,事实上,增加这样一个工艺步骤有背于现时的工业趋势,也会负面影响整体产量。一个更实际的替代方法是,通过诸如有选择性的喷射助焊剂等技术,提供对上助焊剂操作的更好的过程控制。选择性喷射助焊剂可能在使用不同球直径(75 对 300µ)倒装芯片和CSP的混合技术设计中是特别有用的,因为每个元件座的助焊剂数量可由软件控制,为每个元件类型提供确切的助焊剂厚度。

优化滴胶精度、灵活性和过程控制

准确的和可重复的填充剂滴胶是高产量生产环境中最重要的,特别是当要求连续的10mg范围的超小射点尺寸的时候。

填充剂的滴胶要求精确的泵压作用,其流动速率永远不会随粘性、针嘴直径等的变化而变化。填充液体的准确的体积控制可通过使用完全线性的变容泵(positive-displacement pump)来获得,该泵使用一个活塞总是排出所要求的准确体积,不管胶点大还是小。另外,滴胶系统需要结合闭环反馈,使用高精度的比重测量来提供精确的对所滴液体体积的实时控制。最后,滴胶系统必须结合高精度、可编程的运动系统,使得可以对许多不同的滴胶形式作灵活的应用,而且不牺牲整体的产量。

结论

充胶的有效使用要求广泛的掺和许多的因素,包括产品设计问题来适应充胶过程,和包括充胶工艺设计来适应产品需要。针对芯片级设计要求所要达到的准确和灵活的充胶,必然涉及到产品设计者、制造工艺工程师、胶水配制者和滴胶系统供应商之间的合作伙伴关系。

- References

- John H. Lau and S.W.Ricky Lee, Chip Scale Package. McGraw Hill.

- Dr. Reza Ghaffarian, "Key Factors in Chip-Scale Assembly Reliability," Chip Scale Review, Nov. 1998.

- Dr. Reza Ghaffarian, "CSP Assembly Reliability," Circuit Assembly, Sept.1998.

- Communication with H.Quinones, Chief Scientist, Asymtek, Nov. 1999.

- Dr. Reza Ghaffarian, "Key Factors in Chip-scale Assembly Reliability,"

- Rod Martins and Michael Roesch, " Large Flip Chip on Laminate Substrates with Microvias," HP HDI Conference, Aug. 1999.

- M.K. Schwiebert and W.H. Leong, "Underfill Flow as Viscous Flow Between Parallel Plates Driven by Capillary Action" ISHM-USA, Oct. 1995

- Asymtek Flip Chip Calculator is available for free from www.asymtek.com or by calling (800)ASYMTEK.

Steven H. Adamson,is the semiconductor packaging and assembly product manager for Asymtek, a Nordson Co., 2762 Locker Avenue West, Carlsbad, CA 92008-6603; (760) 431-1919; Fax: (760) 431-2678; Web site: www.asymtek.com.